Intel Skylake-S im Detail

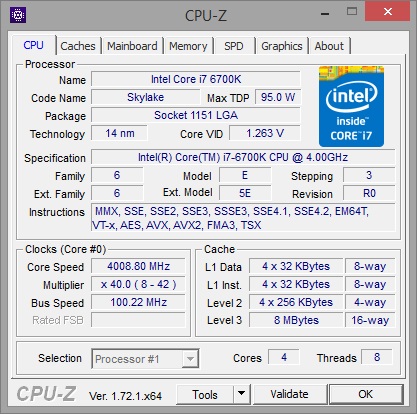

Mit Skylake-S (das S Steht in dem Falle für die Desktop-Ausführung) bringt Intel einige Änderungen mit sich. Vordergründig stehen der Wechsel auf DDR4 sowie der damit verbundene Wechsel auf einen weiteren neuen Mainboard-Sockel (1151) im Raum. Das Top-Modell Core i7-6700K, welches wir künftig auch für alle Mainboard-Test verwenden werden, taktet ab Werk mit 4,0 GHz und per Boost auf 4,2 GHz. Des Weiteren wurde die Strukturgröße von 22nm auf 14nm reduziert, was in der Theorie auch immer eine Verbesserung der Effizienz mit sich bringen sollte. Die 8 MB L3-Cache sind im Vergleich zum Core i7-4790K geblieben. Bei der Anbindung des Chipsatzes kommt erstmals die DMI 3.0 Schnittstelle zum Einsatz, was den Gigatransfer von 5GT/s auf 8GT/s ansteigen lässt. In der Praxis können also mehr Lanes anbunden werden, dazu aber gleich mehr. Die TDP fixiert Intel für den Core i5-6600K und Core i7-6700K auf 91 Watt, auch wenn es im CPU-Z-Screen anders abgebildet wird.

Intel Core i7-6700K - offener Multi + frei wählbarer BCLK (Bus-Takt) - iGPU: Iris Pro 7200

Der wieder im Prozessor integrierte Dual-Channel Memory-Controller kann nun auch erstmals DDR4 mit einer Taktung von 2133MHz verarbeiten. Etliche Mainboard-Hersteller geben ihre Platinen bis zu 3600MHz (OC) und mehr frei, so wie auch beim aktuellen Testmuster dem ASUS Z170-A oder dem MSI Z170A Gaming M5. Neben DDR4 kann der Anwender auch wahlweise auf DDR3L 1600MHz zurückgreifen. Vermutlich wird dies nur in Verbindung mit einem Combo-Board möglich sein, als das man Z170-Platinen ausschließlich mit DDR3L-Anbindung zur Verfügung stellt. Einen, in Relation gesetzten, großen Entwicklungsschritt will Intel mit dem Update der integrierten iGPU vollziehen. Der Hersteller tauft den Chip auf „Intel HD Graphics 530“, was in der Praxis einem Iris Pro 7200 Chip entspricht. Genauere Leistungsangaben ließen sich bis zu diesem Zeitpunkt noch nicht in Erfahrung bringen.

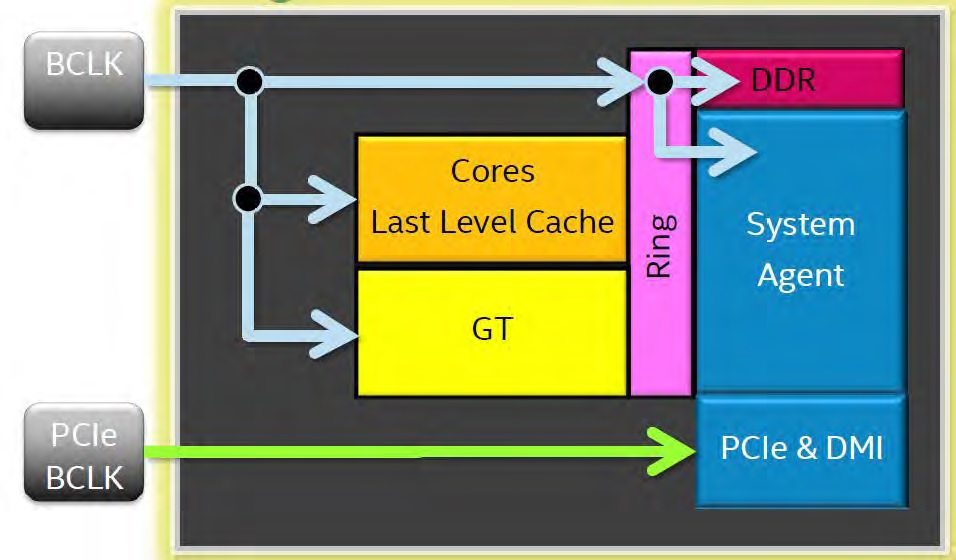

Einen wirklichen Vorteil erlangen die K-CPUs durch die Entkopplung des BCLK vom PCI-E-/DMI-Takt. Dadurch ist es wieder möglich, wie zuletzt bei der Sandy Bridge-Generation gesehen, den Takt „beliebig“ zu variieren bzw. alle Baugruppen separat zu takten. In der Theorie wären so beispielsweise Bus-Taktraten von bis zu 400MHz+ möglich (400 x 12 Multi = 4800Mhz).

Der PCIE- und DMI-Takt sind eigenständig. Dadurch nicht mehr vom BCLK beeinflusst

In der Praxis wird es wohl aber darauf hinauslaufen, dass man sich wieder an das letzte Quäntchen Megahertz herantasten kann und so mehr Stabilität in das Gesamtsystem bekommt. Im Vergleich zum Haswell-Refresh „Devils-Canyon“ entfallen also BCLK-Straps und man kann in 1MHz-Schritten auf Beswerte-Jagd gehen. Der maximal einstellbare Multiplikator beträgt 83x.