AMD hat damit begonnen, die Zen5-Mikroarchitektur durch die GNU Compiler Collection (GCC) zu aktivieren. Die ersten Patches wurden über eine Mailingliste mit dem Titel "Enable support for next generation AMD Zen5 CPU with znver5 scheduler Model" geteilt. Man hätte erwarten können, dass die Unterstützung für Zen5 früher kommt, da die Veröffentlichung von GCC 14 im März und April erwartet wird, was eine typische jährliche Veröffentlichung für diesen Compiler ist. Allerdings neigt AMD dazu, solche Updates sogar nach der Veröffentlichung des neuen Produkts herauszubringen. In diesem Fall beschleunigt AMD tatsächlich die Unterstützung, indem sie zuerst Zen5-Patches einführen, noch bevor das Produkt auf den Markt kommt.

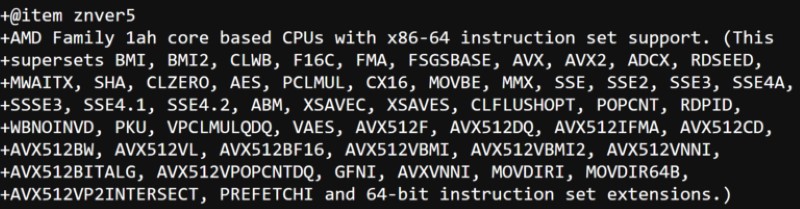

Die Zen5-Architektur wird voraussichtlich später in diesem Jahr ihr Debüt feiern und die Desktop-Serie Granite Ridge sowie potenzielle mobile Varianten aus der Strix Point-Serie bieten. Interessanterweise geschieht der Fortschritt von AMD bei der Entwicklung von Zen5 parallel zu Intels Arbeit an den CPU-Serien Clearwater Forest und Panther Lake, von denen man keine Veröffentlichung noch in diesem Jahr erwarten kann. Gemäß den ersten Patches ist bestätigt, dass AMD Zen5 neue Befehle wie AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT und PREFETCHI unterstützt. Einige dieser Anweisungen werden bereits von der Intel Tiger Lake-Serie unterstützt, waren jedoch in den AMD-Produkten bisher nicht vorhanden.

Bildquelle: videocardz

Es ist großartig zu sehen, dass AVX-512 VP2INTERSECT, das auf der Intel-Seite seit Tiger Lake zu finden ist, berücksichtigt wurde. Befehle wie MOVDIRI und MOVDIR64B sind ebenfalls ein fester Bestandteil seit der Tiger Lake-Serie und es ist löblich, dass AMD nun auch diese Lücke schließt. Die Anweisung PREFETCHI hingegen ist wirklich spannend und wurde bei Konkurrent Intel erst mit der Granite Rapids-Serie eingeführt. Abschließend ist der Befehl AVX-VNNI neu für Zen 5 und entspricht AVX512-VNNI mit VEX-Encoding.

Zen5 Befehlssatz, Quelle: GCC

Der Bericht fügt hinzu, dass der gleiche Befehlssatz für die gesamte Familie der Zen5-Produkte aufgeführt ist, was im Wesentlichen bedeutet, dass Zen5c als eine stromsparendere Variante betrachtet wird und die gleichen Anweisungen unterstützen wird. Da dies eine erste Aktivierung ist, wurde der bestimmte Zeitplanungscode von Zen4 übernommen, bis AMD-Techniker eine aktualisierte Version bereitstellen. Zusätzlich gibt es eine offene Frage bezüglich der Verfügbarkeit von LLVM/Clang-Compilern für Zen5. Patches für diesen Compiler sind bisher noch nicht erschienen.